# AVR SD—Functional Safety Enhanced Microcontroller Family

Stian Sogstad stian.sogstad@microchip.com

#### Designed in compliance with the ISO 26262 functional safety standard for ASIL C / SIL 2 applications

- Dual core lockstep CPU

- 20 MHz CPU clock speed

- Error Controller

- ECC on Flash/SRAM/EEPROM

- 512B User row

- 256B Key storage

- 2.7V 5.5V Supply Voltage Range

- -40°C to 125°C Temp range

#### Special features

- Multi-Voltage IO (MVIO) Integrated level shifters on Port C

- Event system (EVSYS)

- Custom Configurable Logic (CCL)

- Programming and debug interface disable (PDID)

#### Analog

- 2x 10-bit single ended ADCs

- 1x 10-bit DAC

- 3x Analog Comparators

- 2x Zero-Cross Detectors (ZCD)

#### Watchdogs

- Asynchronous Window Watchdog (WDT)

- Synchronous Window Watchdog (SWDT)

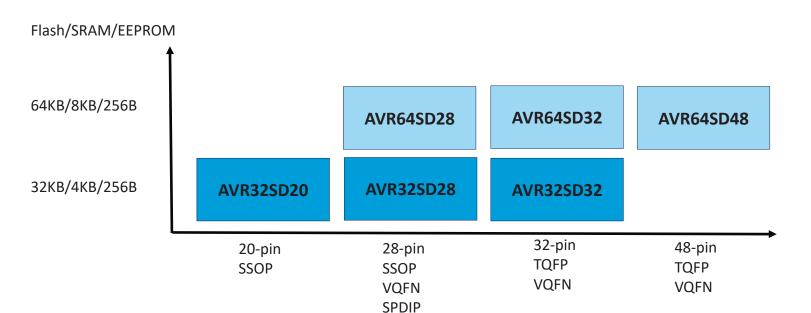

### **Family Overivew**

• 32/64KB Flash

• 4/8KB SRAM

256KB EEPROM

• 20 to 48 pins

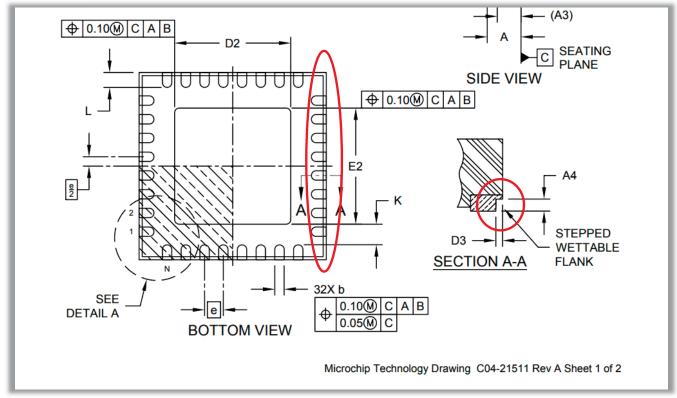

#### **VQFN** with Wettable Flanks

Enabling optical inspection of

the soldering

Usually required by automotive customers

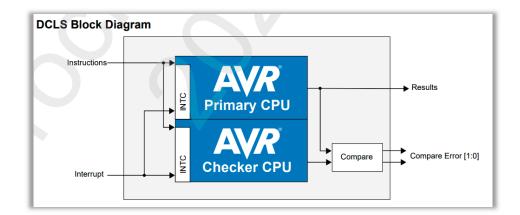

#### **Dual Core Lockstep CPU**

- 20MHz AVR dual-core lock-step CPU

- Same design, different realization by synthesis tool (no I/O delay between cores)

- Physically separated on die

- Diagnostics mechanism

- Full redundancy (>99% coverage)

- Fault injections

- Yes, CPU comparators can be forced to generate a fault

#### Benefit

- Reduce diagnostics code for CPU by 3.5KB

- Reduce diagnostics CPU load by 3.3k CPU clock cycles (per run)

- Increase coverage from 72% to > 99%

- Fault detection time reduced to 1 clock cycle

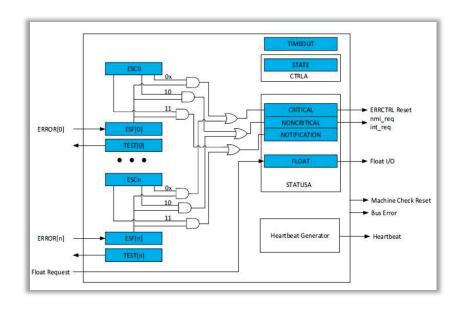

#### **Error Controller**

- Error Controller define response to critical faults

- Flag, Interrupt, non-maskable Interrupt, MCU system reset

- Can be locked after configuration

- Hardware diagnostics

- Critical hardware is redundant

- Fault injection

- Test mode to trigger faults from software

- Benefit

- System integrator controls recovery attempts and error mode response

#### **Error Correcting Code (ECC) on Flash, EEPROM and SRAM**

- SECDED ECC (Single Error Corrected (SEC) or Double Error Detected (DED))

- Detects / corrects data bit faults

- Parity on program data and address BUS bit faults

- Notification on corrected and detected faults

#### Diagnostics mechanism

Redundancy (>99% coverage)

#### Fault injections

Single- and double-bit fault can be injected in data and address

#### Benefit

- Allow system to continue uninterrupted operation with single bit faults per data word

- Allow repair of single bit faults (soft faults only)

- Can be used to detect and correct memory retention issues e.g., accelerated by high-temp operation (Flash only)

### Software Saftey Framework (ASIL C/ SIL2/ ASPISE L3)

- Safety mechanism diagnostics

- Error injection/latent fault checks

- Central error handling manager/unit

- Reset (Fault) Handling

- Middleware to use safety mechanisms

- Scheduling to ensure FDTI and safety system monitoring

| Task Manager Layer |               |  |

|--------------------|---------------|--|

|                    | Task Layer    |  |

|                    | Error Handler |  |

| Middleware Layer   |               |  |

| Driver Layer       |               |  |

| Hardware           |               |  |

#### **Target Applications**

- Battery monitor (current, temperature) for electrical vehicles (ASIL B(D) ASIL D)

- Primary/secondary airbag controller (ASIL C ASIL D)

- Sensor nodes (position sensor, pressure, engine knock, etc.) (ASIL B ASIL C, SIL 1 SIL 3)

- User Interface buttons for steering wheel/levers/joysticks (ASIL B ASIL D)

- Electronic-fuse (ASIL B ASIL C, SIL 1 SIL 3)

- Safety co-processor (fundamantal IO monitor) ( ASIL B ASIL C, ASIL B(D) ASIL C(D), SIL 1 – SIL 3)

- Appliances/HVAC using flammable gas flame detection, monitor gas concentration, pressure/temperature sensing (Class B – Class C)

#### **Simplify Certification Process and Reduce Time to Market**

- Curiosity Nano Evaluation Kit

- MPLAB X Integrated Development Environment (IDE)

- MPLAB Code Configurator (MCC) Melody drivers and code examples

- Certified MPLAB XC8 Functional Safety Compiler license

- ASIL C-compliant software package

- Safety documentation and reports

- Safety manual

- FMEDA report

- Dependent Failure Analyses (DFA)

- Software test report

#### **Summary**

- Family Product Brief

- AVR32/64SD20/28/32/48 Product Brief (microchip.com)

- Product pages (Live by end of the 2024)

- AVR32SD32: <a href="https://www.microchip.com/en-us/product/AVR32SD32">https://www.microchip.com/en-us/product/AVR32SD32</a>

- AVR32SD28: <a href="https://www.microchip.com/en-us/product/AVR32SD28">https://www.microchip.com/en-us/product/AVR32SD28</a>

- AVR32SD20: https://www.microchip.com/en-us/product/AVR32SD20

- Presentation and sell sheet available at the <u>BU Information Portal</u>

- For more information reach out to <u>stian.sogstad@microchip.com</u>

- Marketing Samples: Available Now

- Release to Production: CQ1 2025

## **Thank You**